# **SINGLE 2.2 V OPERATION MMIC POWER AMPLIFIER UTILIZING SrTiO<sub>3</sub> CAPACITORS FOR 2.4GHz WIRELESS COMMUNICATION SYSTEMS**

T. B. Nishimura, K. Yamaguchi, N. Iwata, M. Tomita, K. Takenura

M. Kuzuhara<sup>2</sup> and Y. Miyasaka<sup>1</sup>

Kansai Electronics Research Laboratories, NEC Corporation,

9-1, Seiran 2-Chome, Otsu, Shiga 520, Japan

<sup>1</sup>Fundamental Research Laboratories, NEC Corporation,

<sup>2</sup>ULSI Device Development Laboratories, NEC Corporation,

## Abstract

This paper describes single 2.2 V operation of a two-stage MMIC power amplifier for 2.4GHz wireless local area network applications. The MMIC with 0.76 X 0.96 mm<sup>2</sup> area are composed of n-AlGaAs/ InGaAs/n-AlGaAs FETs with a shallow threshold voltage of -0.24 V and SrTiO<sub>3</sub> capacitors. The capacitors with a high relative dielectric constant of 180 were employed. Under single 2.2 V operation, the developed MMIC delivered an output power of 22.6 dBm (182 mW) and a power-added efficiency of 33.2 % with an associated gain of 22.7 dB at 2.48 GHz.

## Introduction

A small-sized MMIC power amplifier, which can be operated at a single low-voltage DC supply, is required for wireless local area network (WLAN) systems. Although several MMIC power amplifiers for WLAN have been reported[1,2], single low voltage operation of less than 3 V with more than 100 mW output power has not been reported yet. In addition, miniaturization of an MMIC power amplifier chip has been hampered due to the large area of its passive elements. In this paper, a single 2.2 V operation has been accomplished for a two-stage MMIC power amplifier with 0.76 X 0.96 mm<sup>2</sup> area.

## Design and fabrication

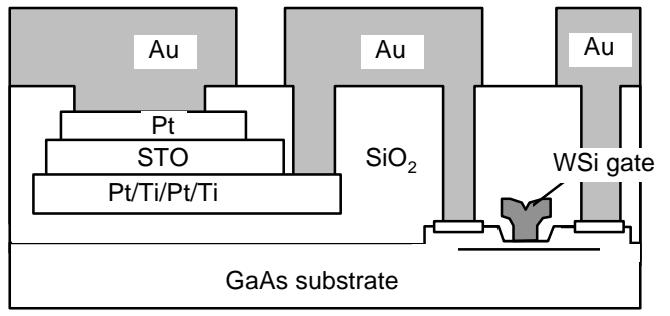

Figure 1 shows a schematic cross section of the developed MMIC. The one-chip MMIC consists of a 2 stage n-AlGaAs/InGaAs/n-AlGaAs heterojunction FET (HJFET) amplifier with input and output matching circuits as well as gate bias circuits utilizing SrTiO<sub>3</sub> (STO) capacitors.

Fig.1 Cross section of the developed MMIC

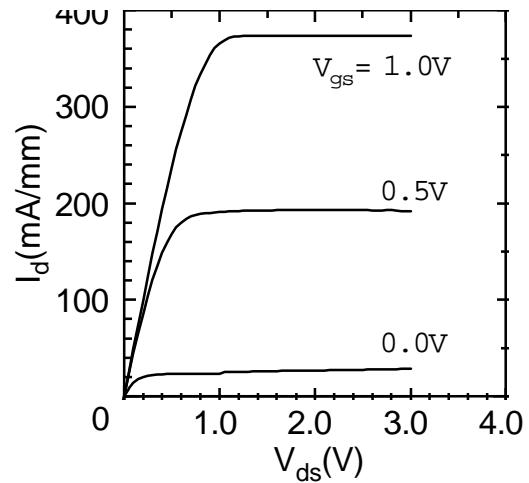

Fig.2 Drain I-V characteristics of the HJFET

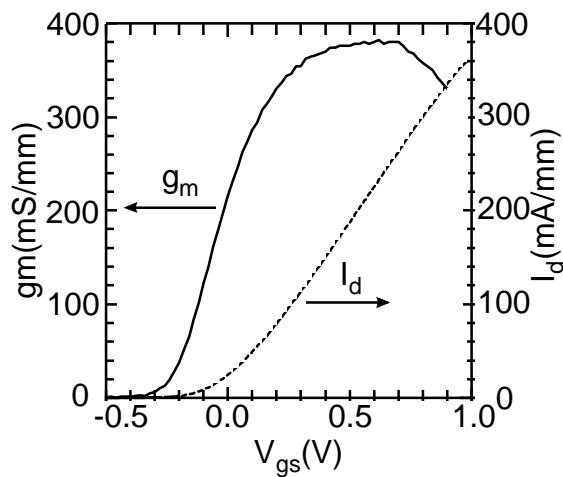

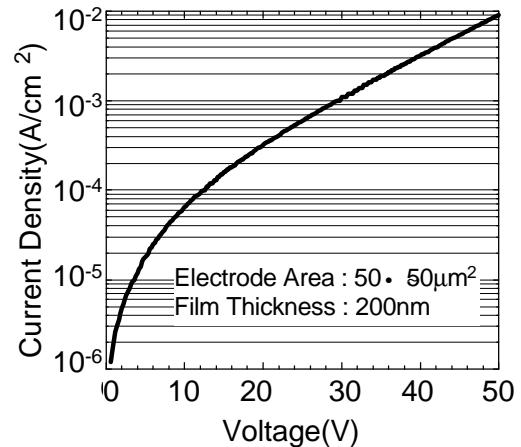

Figure 2 shows the drain current ( $I_d$ ) vs. drain-to-source voltage ( $V_{ds}$ ) characteristics for the HJFET employed. The HJFET exhibited a maximum drain current of 370 mA/mm at a gate-to-source voltage ( $V_{gs}$ ) of 1.5 V. The gate-to-drain breakdown voltage defined at a gate current of -1mA/mm was 20 V. Figure 3 shows the transconductance ( $g_m$ ) and  $I_d$  as a function of  $V_{gs}$  of the HJFET. The threshold voltage ( $V_T$ ) was -0.24 V. This shallow  $V_T$  is essential for single voltage operation[3]. A double recess structure was fabricated by dry etching with an electron cyclotron resonance source, and the resulting standard deviation of  $V_T$  was as small as 20 mV on a 3 inch wafer. The capacitor consists of a Pt/Ti/Pt/Ti base metal electrode, a 200 nm-thick STO film and a Pt top electrode. This base electrode has high tolerance against ion-milling for capacitor fabrication, resulting in low series resistance[4]. The STO film was deposited at a substrate temperature of 450 °C before the HJFET fabrication. The STO film exhibited relative dielectric constant ( $\epsilon_r$ ) of 180. The capacitor fabricated in this process was reported to exhibit a high  $\epsilon_r$  up to 20 GHz[4]. Figure 4 shows the I-V characteristics of the STO capacitor whose electrode area is  $50 \times 50 \mu\text{m}^2$ . The breakdown voltage defined at a  $10 \text{ mA/cm}^2$  leakage current was more than 50 V. A 5.3  $\mu\text{m}$ -thick Au layer was plated on the electrodes of capacitors and inductors to reduce DC and

Fig.3  $g_m$  and  $I_d$  vs.  $V_{gs}$  of the HJFET

Fig.4 I-V Characteristics of the STO capacitor

RF losses.

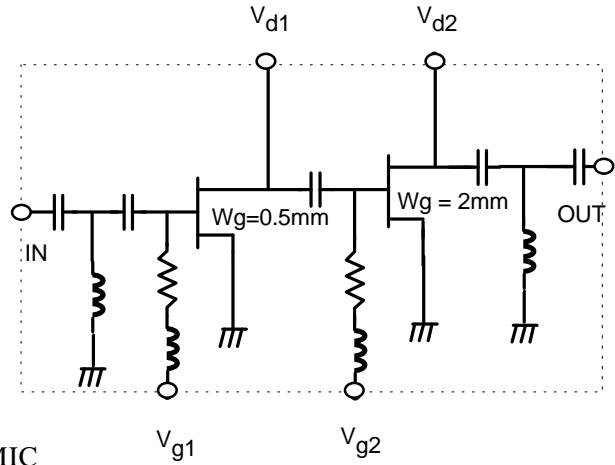

Figure 5 shows a circuit diagram of the MMIC

Fig.5 Circuit diagram of the MMIC power amplifier

power amplifier. The gate widths for the first stage and the second stage HJFETs are 0.5 and 2.0 mm, respectively. The input matching circuit is designed for maximum gain, and the output matching circuit is designed for maximum output power. For the output matching circuit, a series C and shunt L matching circuit with a coupling capacitor (CLC circuit) is employed. Since small area capacitors are available employing high  $\epsilon_r$  STO films, the output matching circuit area is  $0.05 \text{ mm}^2$ , whereas the area of a conventional series L and

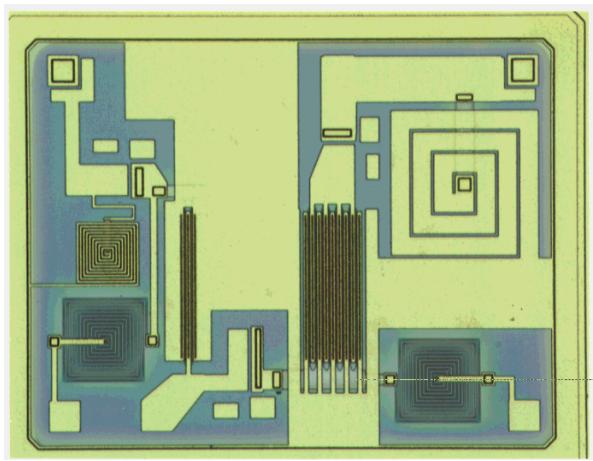

Fig.6 Chip photograph of the MMIC power amplifier

shunt C matching circuit with a coupling capacitor (LCC circuit) employing  $\text{SiN}_x$  capacitors was  $0.18 \text{ mm}^2$ . Thus the CLC circuit with STO capacitors reduces 70 % of output matching circuit area as compared to the conventional one. Figure 6 shows the chip photograph for the MMIC power amplifier. The chip size is  $0.0796 \text{ mm}^2$ .

## MMIC Power Performance

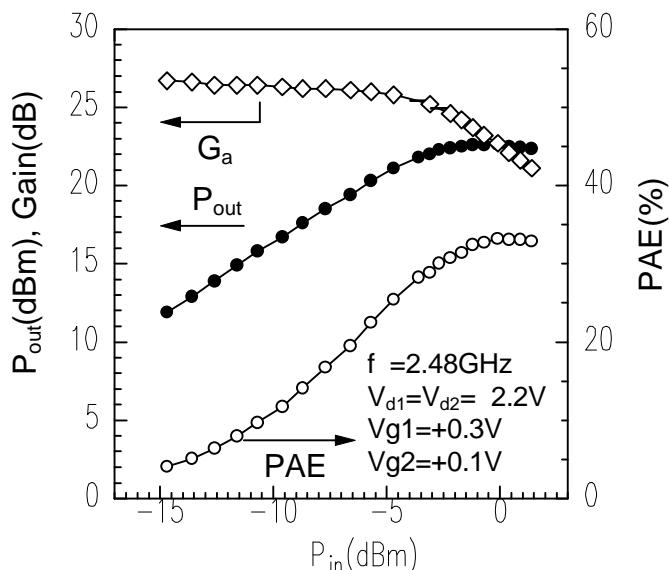

The MMIC amplifier was operated at a drain supply voltage ( $V_{d1}$ ,  $V_{d2}$ ) of 2.2 V with gate bias voltages for the first FET ( $V_{gs1}$ ) of +0.3 and the second FET ( $V_{gs2}$ ) of +0.1 V. Bias voltages can be supplied by two Ni-MH battery cells without using a negative bias circuit. Figure 7 shows a 2.48 GHz power performance of the MMIC amplifier. The MMIC exhibited an output

Fig.7  $P_{out}$ , PAE and  $G_a$  vs.  $P_{in}$  for the MMIC amplifier

power of 22.6 dBm (182 mW) and a power-added efficiency of 33.2 % with an associated gain of 22.7 dB. To our knowledge, this is the first report of a GaAs MMIC power amplifier operated at single low voltage less than 3 V for WLAN applications.

## Summary

A single 2.2 V operation two-stage MMIC power amplifier with  $0.76 \times 0.96$  mm<sup>2</sup> area has been developed. n-AlGaAs/InGaAs/n-AlGaAs FETs with shallow  $V_{of}$  of -0.24 V and SrTiO<sub>3</sub> capacitors with a high  $\epsilon_r$  of 180 were employed. Operated at single 2.2 V, the MMIC delivered

22.6 dBm (182 mW) output power and 33.2 % power added efficiency with 22.7 dB associated gain at 2.48 GHz. The developed MMIC amplifier is promising for miniaturized WLAN applications.

### **Acknowledgments**

The authors would like to thank N. Tawarayama for the STO deposition, M. Funabashi and H. Oikawa for useful discussions and suggestions. We are also grateful to Drs. T. Ito, N. Shohata, H. Abe, T. Uji and M. Ogawa for encouragement.

### **References**

- [1] K. Kobayashi, T. Maniwa, Y. Aoki, "GaAs MMIC for 2.4 GHz wireless LAN applications," ICICE Trans. Electron., vol.E79-C, 5, 1996, pp.705-708.

- [2] D. Fitzgerald, Y. Tajima, R. Donahue, M. McPartlin, R. Binder, M. Tsai, G. Chu, J. Wendler, "A MMIC 2.4 GHz Transmitter and 5.78 GHz Receiver for Wireless LAN Applications," 1995 MTT-S Symp. Tech. Wireless Appl. Dig., 1995, pp.21-25.

- [3] N. Iwata, K. Inosako and M. Kuzuhara, "Single Low-Voltage Operation of Power Heterojunction FETs for Digital Cellular Applications," Inst. Phys. Conf. Ser. No145, 1995, pp. 813-816.

- [4] T. B. Nishimura, N. Iwata, K. Takemura, M. Kuzuhara, Y. Miyasaka, "SrTiO<sub>3</sub> Capacitor with Relative Dielectric Constant of 200 on GaAs Substrate at Microwave Frequency," Jpn. J. Appl. Phys. pt.II. vol.35, No.12B, 1996, pp. L1683-L1684.